Streaming video, cloud services, and mobile data are fueling the continuous growth of global network traffic. To meet this demand, network systems must deliver faster line rates and process millions of packets per second efficiently. In such systems, packet arrival order is random, and each packet requires multiple memory accesses for processing. This results in a need for hundreds of millions of memory operations per second to perform lookups or update statistics in the forwarding table.

The packet rate directly correlates with the random access rate. Modern network devices require high random access performance (RTR) and wide bandwidth to keep up with the ever-increasing traffic. RTR refers to the number of fully random memory accesses—either read or write—that can be performed per second. It’s measured in millions of transactions per second (MT/s), and it's independent of the amount of data processed during each access.

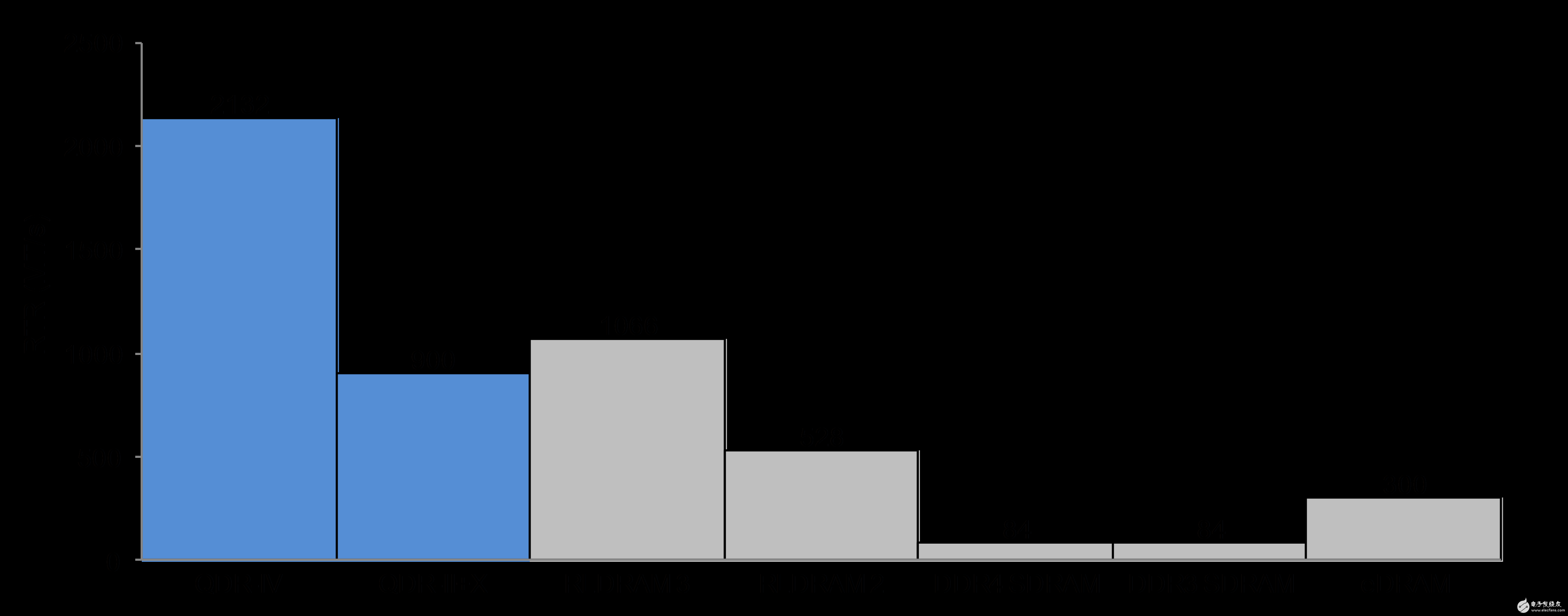

Today’s high-performance DRAMs struggle to match the random access demands of modern network systems. That’s where QDR-IV SRAM comes in. Engineered for high-performance networking, QDR-IV delivers industry-leading RTR performance, making it ideal for critical tasks like updating statistics, tracking flows, scheduling packets, and performing table lookups. As shown in Figure 1, QDR-IV outperforms other memory types by nearly double, even when compared to the highest-performing alternatives.

In the first part of this series, we’ll take a closer look at two variants of QDR-IV memory: XP and HP. These versions differ in their operating frequencies and capabilities, particularly in how they handle grouping operations.

**Different Types of QDR-IV: XP and HP**

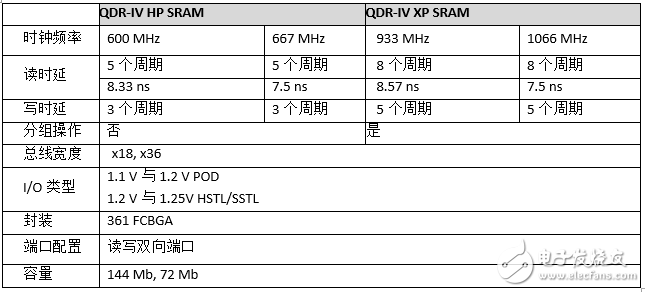

There are two main types of QDR-IV: HP and XP. The HP variant operates at lower frequencies and does not support grouping operations. For applications that demand the highest possible performance, the XP version supports advanced grouping schemes and runs at higher clock speeds.

The read and write latency of QDR-IV depends on its operating frequency. Table 1 outlines the different operating modes and the corresponding frequency ranges.

**QDR-IV SRAM Architecture**

The QDR-IV SRAM features two independent ports—Port A and Port B. Because these ports can be accessed simultaneously, the device achieves maximum random transaction rates regardless of the read/write combination. Each port uses a double data rate (DDR) address bus, with Port A latching its address on the rising edge of the input clock (CK), while Port B latches on the falling edge of CK or the rising edge of CK#.

Control signals (LDA#, LDB#, RWA#, RWB#) operate at a single data rate (SDR) and determine whether a read or write operation is executed. Both data ports (DQA and DQB) use DDR interfaces, allowing for efficient data transfer. The device employs a 2-word burst architecture and offers data bus widths of ×18 or ×36, providing flexibility for various system designs.

O.D114MM Hydraulic Dc Motors,O.D114MM Hydraulic Dc Motor,O.D114MM Dc Hydraulic Pump,O.D114MM Dc Hydraulic Pump Motor

Wuxi Jinle Automobile Motor Factory , https://www.wxjldj.com