Embedded systems are increasingly used in a wide range of applications, and they often operate in environments that can be harsh or prone to interference. These conditions can significantly impact the stability and reliability of the system. A key factor in maintaining system stability is the proper implementation of the reset mechanism. By carefully designing the reset circuit and strategically applying reset operations, the overall performance and reliability of the embedded system can be greatly improved. This paper explores the practical applications and design considerations of reset mechanisms, drawing from real-world project experiences to highlight their critical role in ensuring system stability.

In the operation of an embedded electronic device, if the program runs out of control or jumps unexpectedly, the hardware can signal a reset through either manual or automatic means, restoring the software to a predefined segment of code. This process is known as a reset, and the signal sent to the hardware interface is referred to as the reset signal. To address instability caused by internal factors such as clock oscillation issues or external factors like radio frequency interference, both the software and hardware of the embedded system must be appropriately protected. The reset function serves as an effective safeguard. However, it's also important to note that improper reset operations can themselves introduce instability, making careful design essential.

This article draws on the author’s personal experience to emphasize the importance of reset mechanisms. By using reset functions cleverly, the system can achieve greater stability and reliability.

**1 Reset Methods and Approaches**

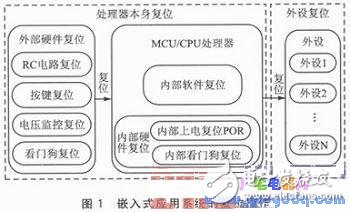

In an embedded application system, the reset process involves two main components: the reset of the processor itself and the reset of the peripheral modules connected to the system, as illustrated in Figure 1.

Generally, there are two primary types of reset: hardware reset and software reset. A hardware reset is initiated through physical signals, such as a power-on pulse, button press, voltage monitoring, or watchdog timer. These signals are typically routed into the RST pin of the system. A software reset, on the other hand, is triggered within the software framework to reinitialize the system.

Depending on whether the reset is internal or external to the processor, hardware resets can be further categorized into on-chip and off-chip resets.

From a signal level perspective, hardware resets can be classified as either high-level or low-level. In a high-level reset, the reset is active when the signal is high, and the reset completes on the falling edge of the pulse. In a low-level reset, the signal is active when low, and the reset completes on the rising edge. Most embedded systems use low-level resets due to the lower current consumption of TTL circuits at this level.

**2 Power-On Reset Implementation and Stability Design**

**2.1 Power-On Reset (POR)**

Power-On Reset (POR) is a fundamental process that ensures the system starts up correctly. When the system is powered on, the POR circuit generates a reset signal for a certain duration until the power supply stabilizes. During this time, all logic cells and modules within the processor are reset, and internal configurations such as memory controllers, interrupt controllers, and I/O pins are initialized.

Many microcontroller units (MCUs) include built-in POR circuits. For example, the MCU shown in Figure 2(a) has an internal POR that activates during startup. The timing diagram in Figure 2(b) illustrates how the reset signal is generated and maintained.

Some processors require an external RC delay circuit to generate a POR signal. The width of the reset pulse depends on the RC time constant. If the capacitor is too large, the reset time becomes too long; if it's too small, the reset may not be sufficient to stabilize the system.

**2.2 Power-On Reset Failure and Solutions**

In practice, power-on reset failures can occur due to various reasons such as electrical noise, power fluctuations, or accidental power interruptions. If the voltage drops briefly and then recovers, the system may fail to restart properly because the reset condition isn't met. Similarly, if the power supply switch-off period is too short, the reset may not be reliable. Surge events can also cause the reset pulse to be missed after the surge ends.

To mitigate these issues, designers often adjust the reset threshold to fall within the normal operating range of the processor. Extending the reset pulse duration ensures the system remains in reset long enough for the power to stabilize. Additionally, a delay is introduced before the reset signal is released to prevent jitter caused by power transitions. Some systems also add a diode discharge circuit to the RC network, allowing the capacitor to discharge quickly during voltage drops, ensuring a reliable reset even during brief power glitches.

**2.3 Case Study: MCU Startup Instability in a Fast-Switching System**

In a ZigBee IoT project using a ZigBeeSoC chip, the system was observed to rapidly shut down and restart, causing instability during the boot process. After adding trace information to the software, it was found that the MCU did not initialize properly when the system was turned on and off quickly. As a result, the system failed to enter the required initialization routine and main loop.

By introducing a delay between power cycles, the system could start up reliably. This issue highlights a common challenge in embedded systems: insufficient reset can lead to erratic behavior upon power-up. Proper reset design is therefore crucial to ensure stable and predictable system operation.

Cixi Xinke Electronic Technology Co., Ltd. , https://www.cxxinke.com